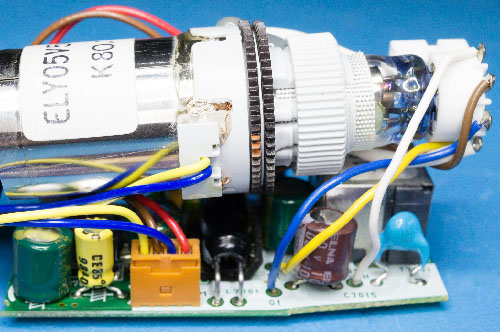

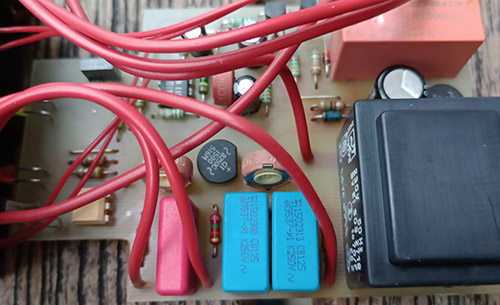

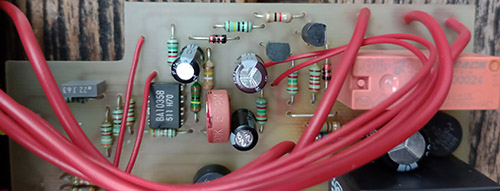

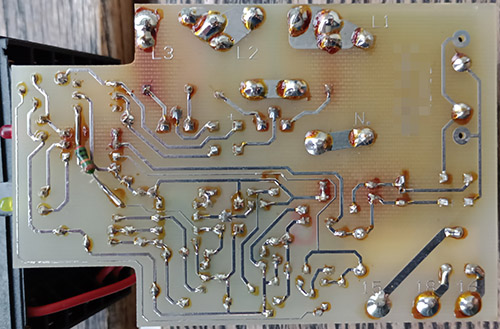

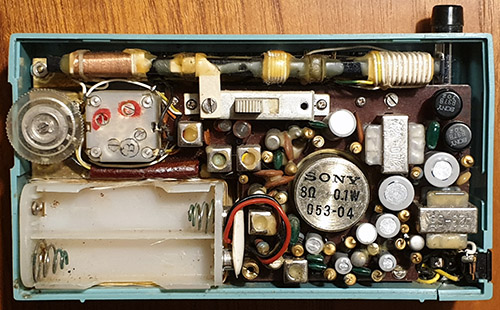

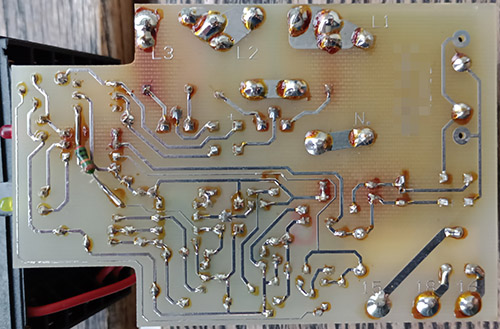

The “wäre” for July 2023 is shown below.

Thanks to zebonaut for submitting this ware. According to him, this was fished out of a dumpster in Germany, hence “wäre” (and yes, it’s a nonsense word, but I also think it’s cute). We had a little chuckle over the ware’s construction (or more precisely, the lack thereof). You could say, “they don’t build them like they used to” — could something like this pass certification in modern Germany? Well, it seemed to have at least passed the test of time, since it only recently found its way into a dumpster, and the rating label indicates a manufacturing date from the 14th week of 1996.

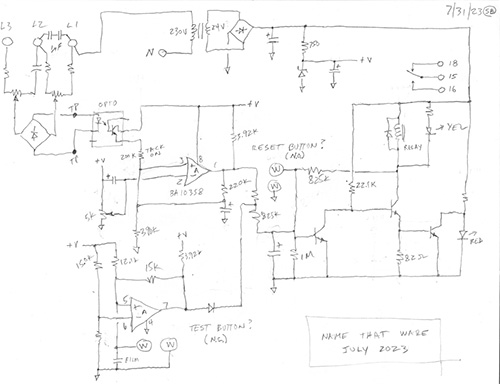

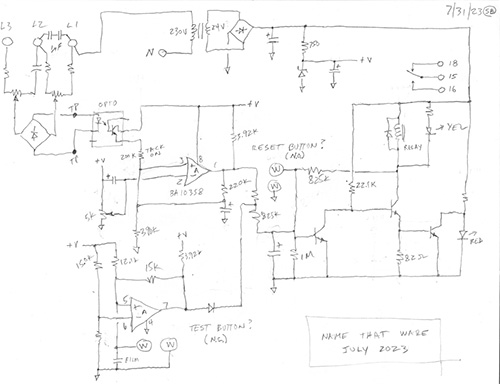

Update Aug 7

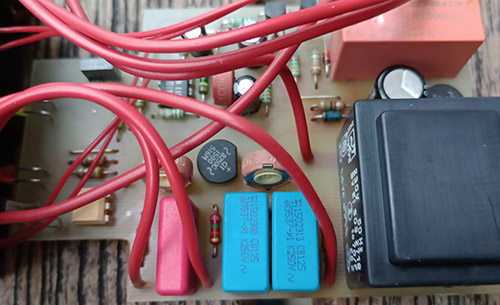

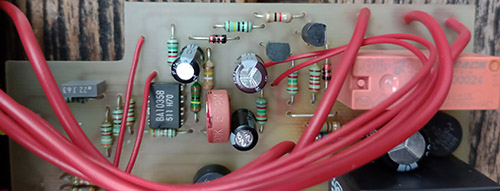

FETguy has contributed schematics for the ware, which he reverse engineered by hand:

A big thanks for contributing these! The spirit of Name that Ware is to inspire people to learn about electronics by taking things apart and observing their construction — and reverse engineering schematics is the asymptotic limit of that spirit!