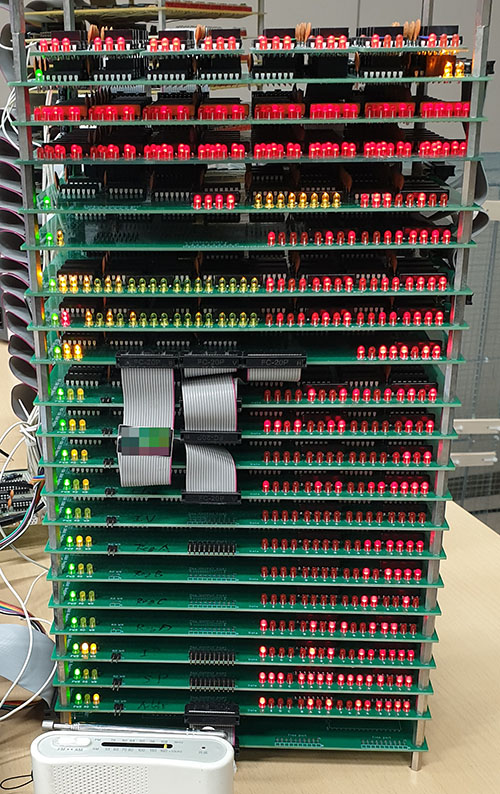

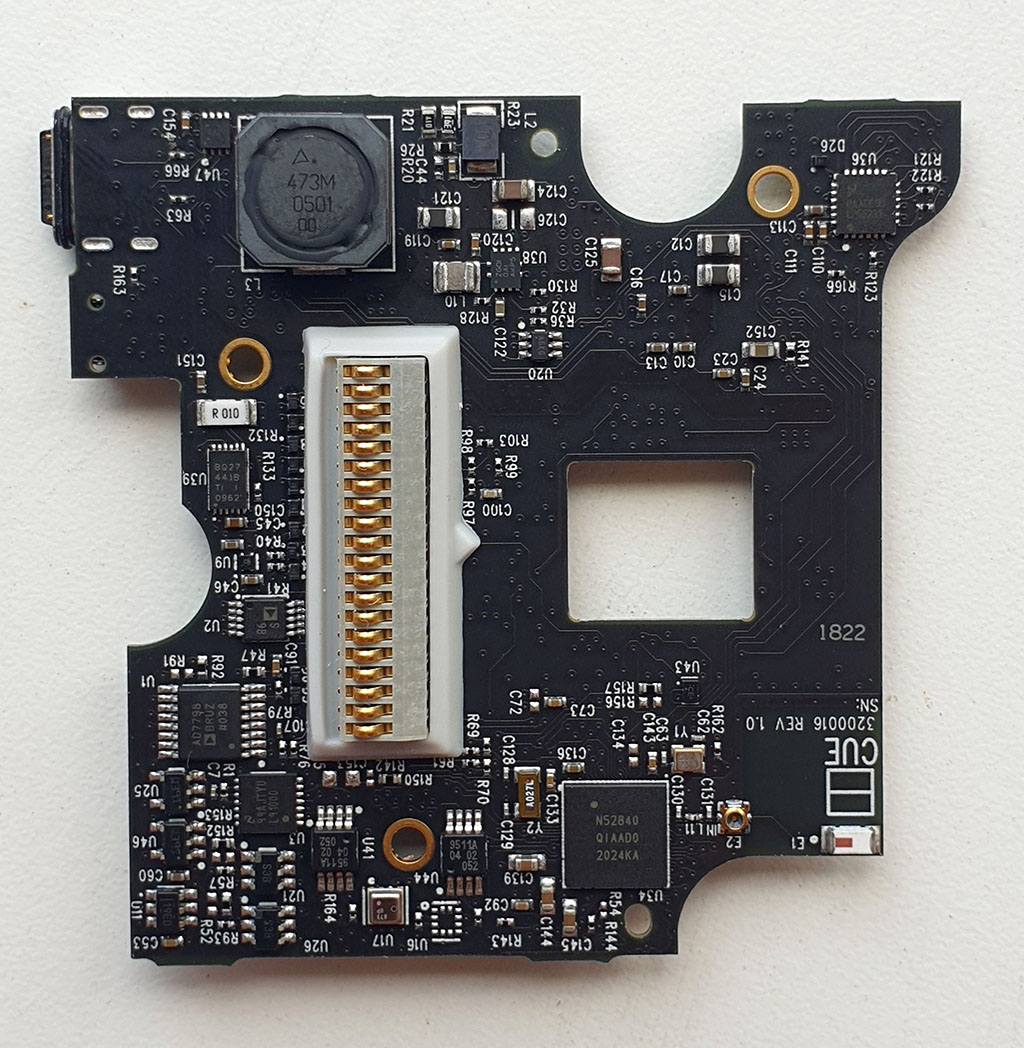

The Ware for November 2024 is the NLP-16A by cherry-takuan. It’s a bespoke 16-bit CPU made entirely from 74HC00 NAND gates.

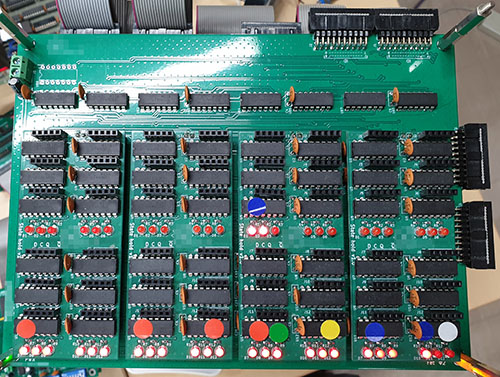

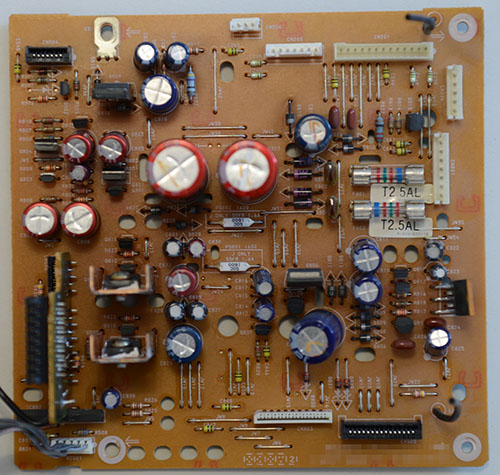

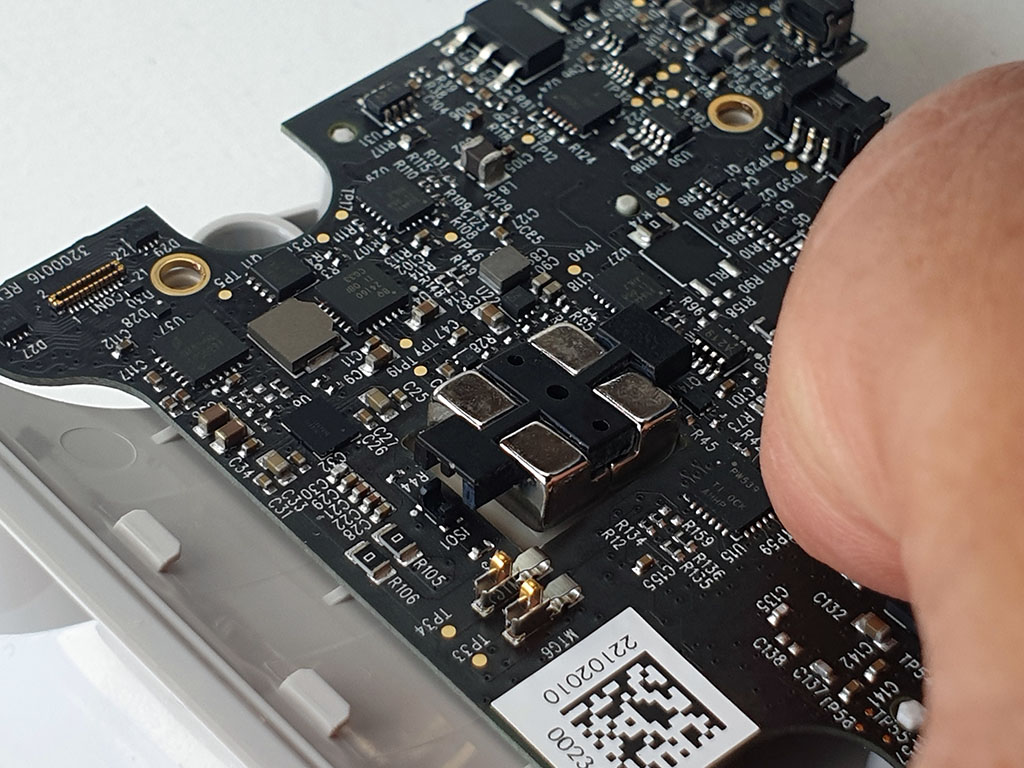

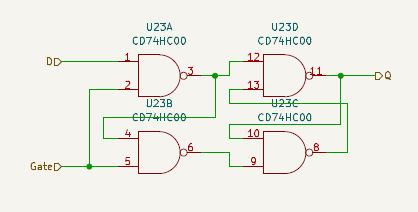

Even the D-flip flops are made from NAND gates:

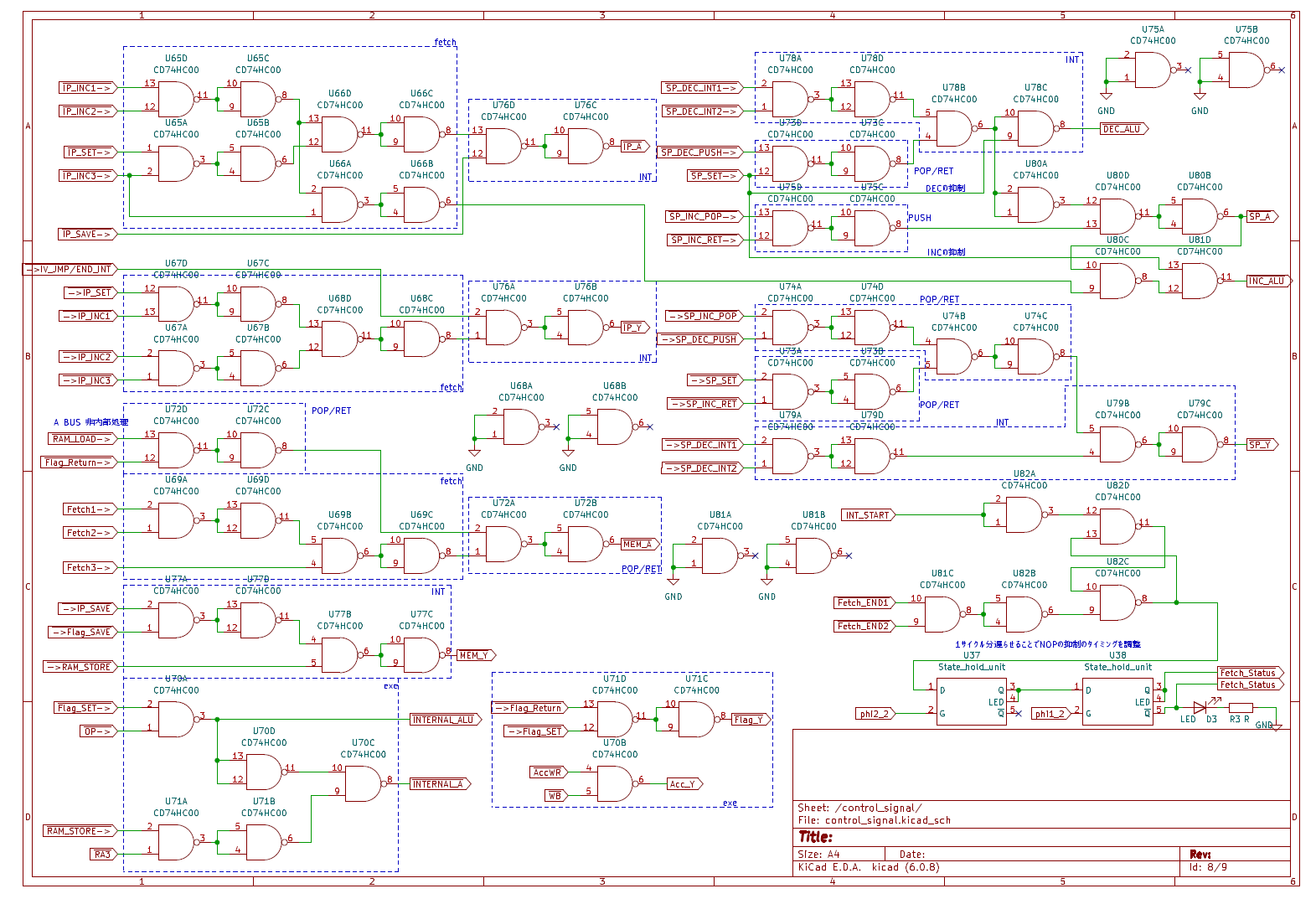

Lots and lots of NAND gates…

I got to meet the maker, who goes by Cherry Takuan, at the Chiba Institute of Technology‘s 75th annual student festival. The NLP-16A was on display in a corner of the Denken electronics club (there’s also a rival club at the event, CITera). I was a little in disbelief at first, but after a bit of hemming and hawing I convinced myself this was in fact a full 16-bit CPU made out of nothing but NAND gates (the I/O card and RAM/ROM are separate). It’s double-cool in that the whole thing is up on github (here’s the schematics) and all the tooling (assembler, demo applications, etc.) are there as well. This was apparently a high school project that grew out of control and he’s now on his 6th year working on it. I wonder if he’d be interested in making a version in SKY130 with eFabless or TinyTapeout. Could stick with the “entirely NAND gate” theme, even in silicon, because why not?

I love this kind of stuff, and it’s heartening to know there’s still engineering students who have a hankering to build stuff out of nothing but NAND gates and solder — and will take the time to do it, instead of chasing the latest AI-crazed startup idea. In retrospect, I could grow into who I am today only because I cut my teeth on gritty projects like this (although not nearly as ambitious!), back when I was his age.

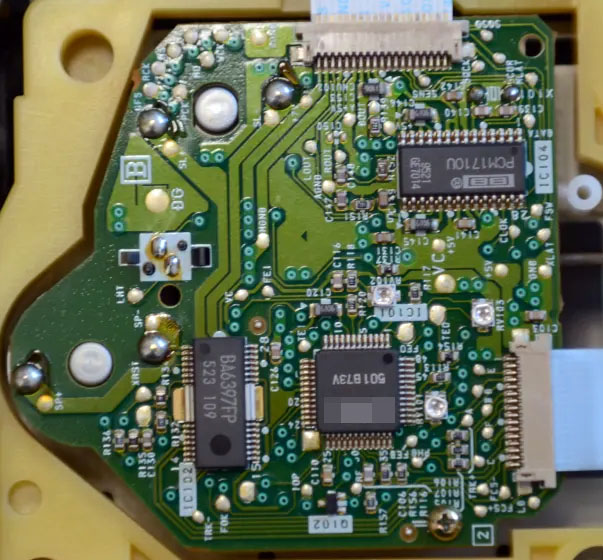

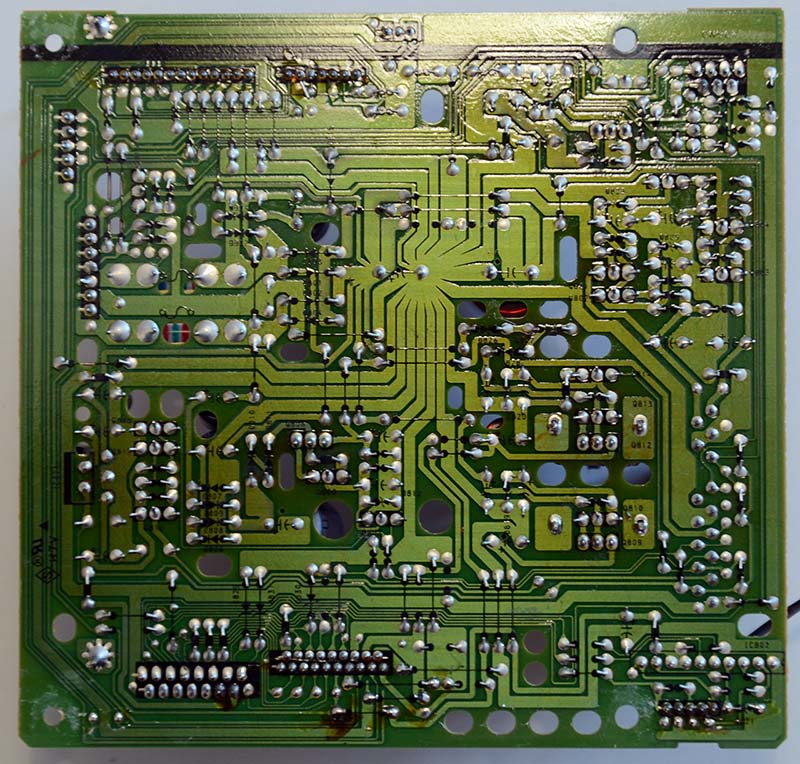

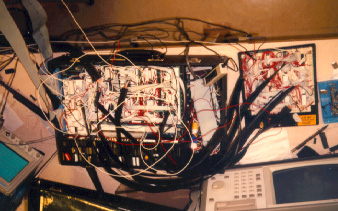

For example, above is a 48-bit wide VLIW audio DSP I made for a “6.111” lab project when I was an undergraduate at MIT…I “cheated” (compared to cherry-takuan’s all-7400 flex) and used some PLA devices, ROMs, and SRAMs to improve density. Unfortunately it was all breadboards so it was ripped up shortly after the class ended. This potato-quality photo is all I have left of it, but this was all pre-Internet, and about as good as we could do back then to preserve a design for sharing if you were a cash-strapped undergraduate with nothing but disposable film camera (remember those?).

Congrats to Alastair for nailing this one. Email me for your prize!