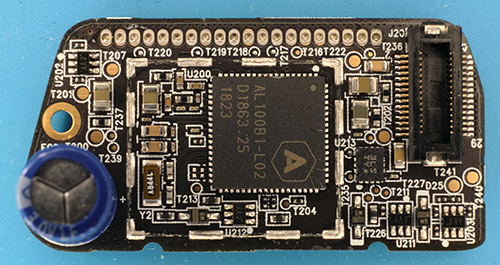

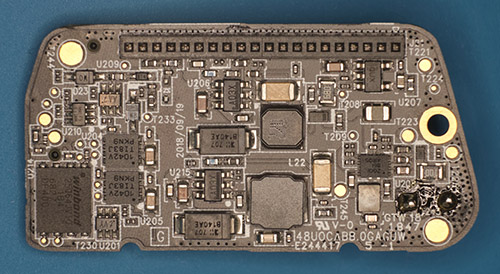

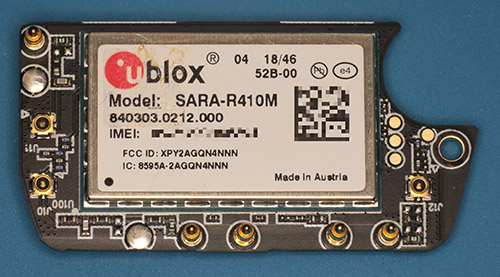

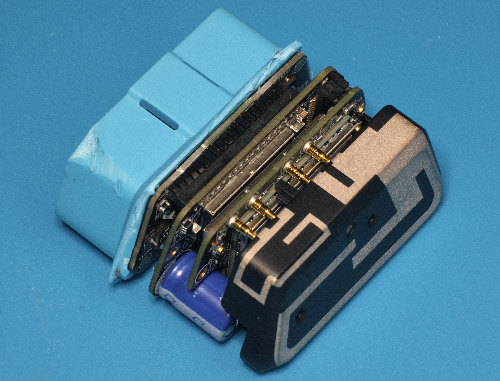

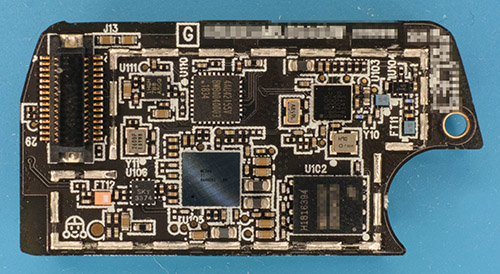

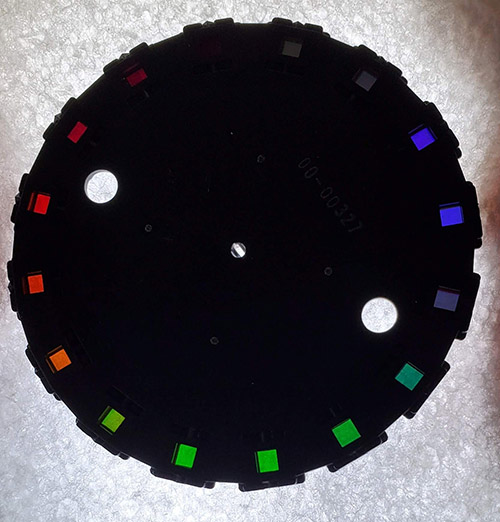

The ware for June 2023 is shown below.

This ware should be possible to match to an exact model number, based on this photo alone — if not simply because in its era there were fewer consumer electronics devices to choose from.

I tested the image against Google Image search and this particular crop of the ware seems to foil any exact matches. However, if you do manage to find an exact hit with a simple image search engine query, I’d be curious to know what you’re using, so I can use this to test against future wares.

According to the original owner, this ware cost almost a month’s wages back when it was purchased!